RISC-V, an open standard instruction set architecture (ISA), has captured the imaginations of engineers and innovators worldwide due to its simplicity and accessibility. This architecture offers simplified instructions, enabling designers to develop customized processors. Its open-source nature makes the RISC-V architecture widely used among designers, creating extended instructions and configurations for specific applications.

Though RISC-V is quite popular, many design and verification challenges will arise as this architecture evolves. A significant concern is the potential fragmentation in RISC-V system integration. During the exploration of RISC-V microarchitectures, RISC-V variants created by multiple vendors may not be compatible with each other. Furthermore, as RISC-V ecosystem matures, the complexity of RISC-V designs also scales up. This growing design intricacy calls for an enhanced RISC-V verification procedure.

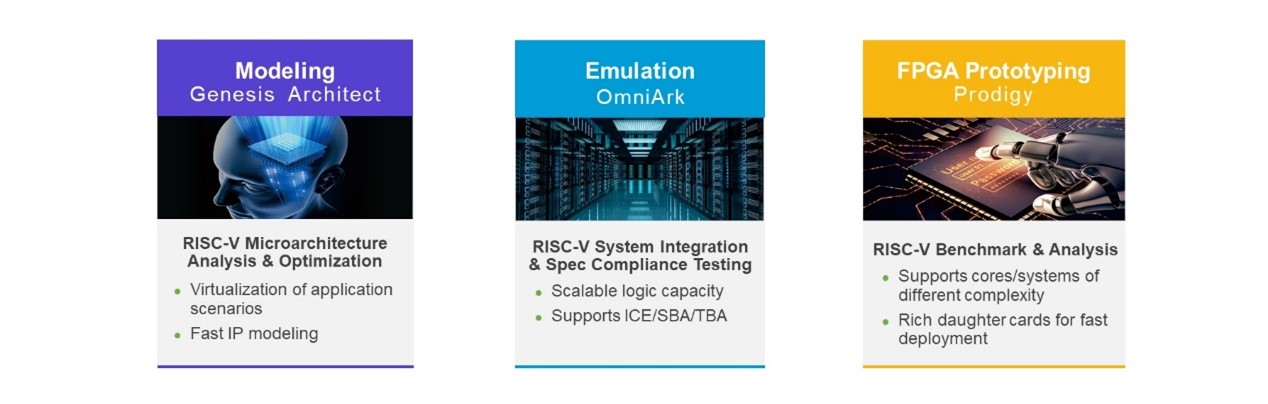

S2C provides multiple plans for diverse RISC-V requirements, including Genesis Architect, OmniArk Emulation, and Prodigy FPGA-based Prototyping. Genesis Architect helps developers to explore RISC-V microarchitecture analysis and optimization. OmniArk works on RISC-V system integration and verification primarily, and later will be used for specification performance testing. Prodigy focuses on RISC-V design verification and benchmarking. Most of these RISC-V needs are addressed through FPGA prototyping.

Prodigy, S2C’s complete FPGA prototyping solutions, benefits the RISC-V industry in the verification, software development, benchmarking, and demonstrations. Prodigy enables early software development in parallel with hardware development, shortening the R&D cycle. It also provides software benchmarking to test whether the RISC-V design meets the desired performance. Additionally, Prodigy is a good choice for developers to demonstrate their RISC-V designs, highlighting design capabilities and engaging users.

In the "XiangShan" high-performance open-source RISC-V processor project, S2C provides the Prodigy S7-19P Logic System to facilitate the project’s functional verification. S7-19P, an ideal FPGA prototyping solution, supports SPEC benchmarking, I/O verification, and BSP driver development for the XiangShan project. With this solution, the XiangShan team can start software development early while conducting hardware validation. This parallel approach enables the project to greatly reduce the time needed for software development after tape-out.

The RISC-V ecosystem presents both exciting opportunities and challenges. As the architecture matures and diversifies, S2C offers plans to address RISC-V design needs and the fragmentation issue. By providing tools and strategies for early software development and benchmarking, S2C enables developers to choose the most fitting RISC-V IP cores. S2C's commitment to RISC-V demands will ensure a better design and verification process for all involved.