Designing the right product is more important than designing the product right. The ability to explore different design ideas early and provide a working demonstration to customers earlier will significantly increase the success of a product launch.

The sooner that problems in the design can be identified the easier and faster it is to correct-possibly shaving weeks/months of development time. Although simulation offers you an abstract view of the design, simulation cannot provide a complete model for early access to the design. Nothing compares to seeing the design working on hardware. The ability to perform an early evaluation the architecture of the processor, cache size, and bus width with the rest of the design implemented in the FPGA is critical.

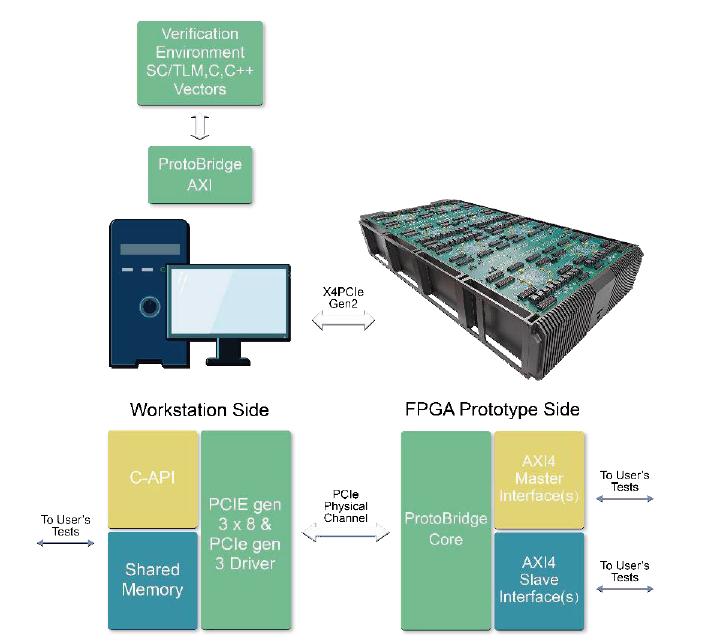

To facilitate early Design Exploration, ProtoBridge from S2C provides a high bandwidth data channel between software models running on a host PC and the FPGA prototyping hardware. ProtoBridge consists of CAPI for users, software drivers for the host PC, PCIe-based connectivity hardware between the host PC and the Prodigy Logic System, and a PCIe-to-AXI bridge to interface with the user design blocks.

S2C announced Genesis software to deliver a hybrid SoC architecture exploration solution that reuses available RTL-based blocks to accelerate model construction and complex simulations. Genesis’s VisualSim interfaces with S2C’s FPGA Prototyping solution, Prodigy Logic System, to model a functional block of the design in which the FPGA prototype acts as a sub-model and provides accurate simulation responses for architecture exploration.

The collaboration enables the RTL behavior modeled through FPGA prototyping, to be easily integrated into an ESL model to create a virtual platform. The model can be simulated to gather metrics on response times, throughput, power consumption, and correctness of data values.