Early IP Verification without the complete SoC design

IP blocks connected to the AXI bus can be verified without processor cores or peripheral blocks

Early algorithm/architectural exploration can be performed on the FPGA while taking advantage of the FPGA environment's speed performance

Shorten Design Verification Time with a high-throughput channel

Transaction-level verification is utilized to ensure system-level result accuracy

C-code is used as a stimulus to reduce the time and effort in creating RTL test benches

Achieve High Product Reliability with improved test coverage

Create corner test cases in software and run exercises on an FPGA-based prototype

Run high-performance regression tests on an FPGA-based prototype with vectors stored in host computers

Eliminate Resource & Expertise Constraints by removing the need for the creation of additional specialized hardware and software

Prodigy ProtoBridge Reuse Across Multiple Projects as the flexibility of Prodigy ProtoBridge makes it ideal for any design

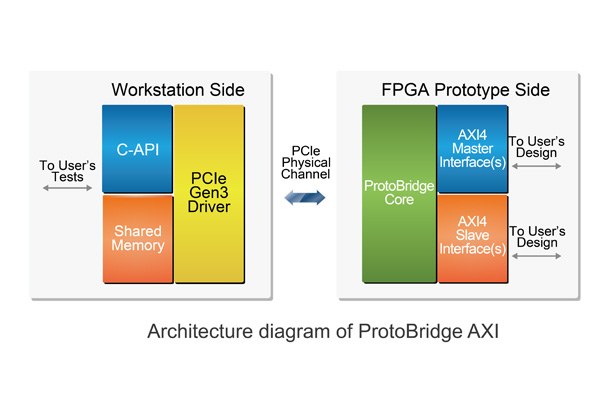

AXI-4 Bus Protocol Between Host PC and FPGA

Instantiation of AXI-4, AXI4-Lite, AXI-3 and AHB bus connections on FPGA ports

Configurable data width from 32-bit to 1024-bit

Support for an independent clock for each Master/Slave instance

Exercise of Large Amounts of Verification Data at High Speed

Transmission through 8-lane PCIe Gen3 between Host PC and FPGA

Massive data transfer from Host PC to FPGA up to 4000 MB/s

Support for direct and DMA access modes

Rich Coverage of C Function Calls Between Host PC and FPGA

System initialization function calls to manage the tool environment

Interrupt control function calls to identify the source of an interrupt signal for C-API's follow-up actions

Data read/write function calls to communicate with and operate the FPGA circuit

DMA transfer function calls to perform DMA operations for large amounts of data

Get World-Class Support to help design teams with any issues that arise-something not available with in-house solutions leaving design teams to fend for themselves