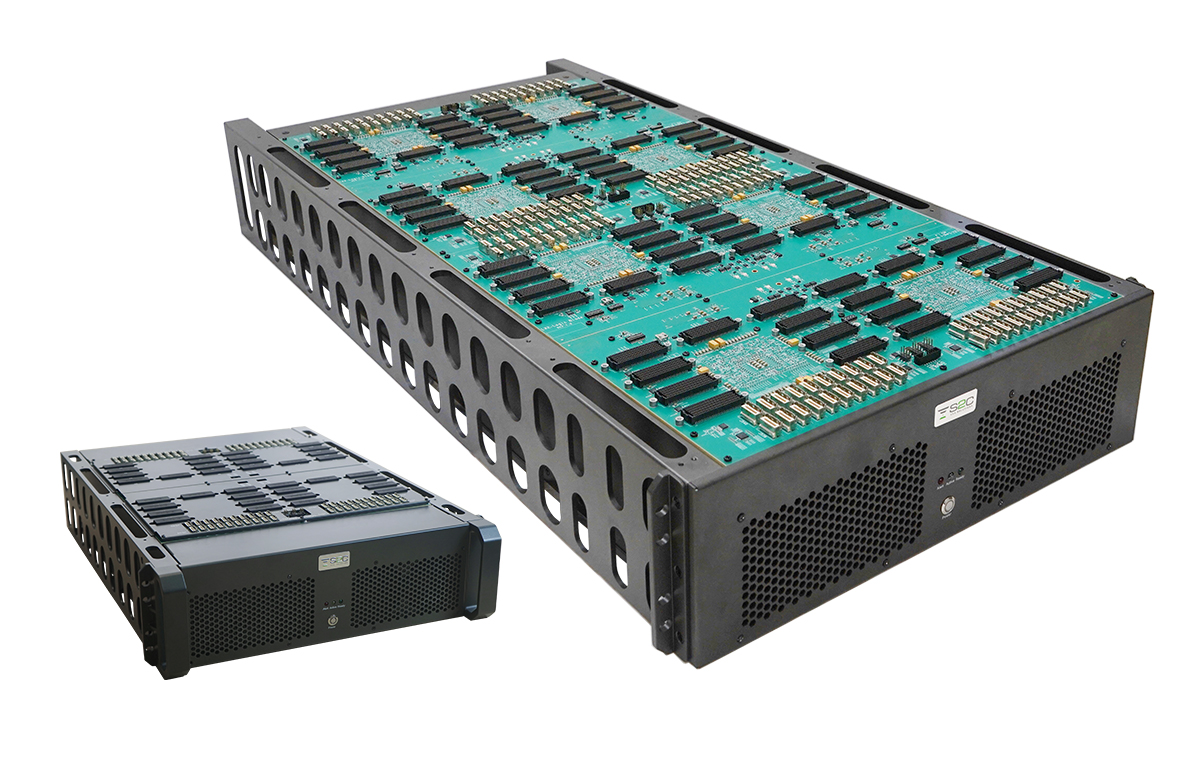

Prodigy™ Logic Matrix is a high-density FPGA prototyping platform architected from the ground up to meet today's needs for both hyperscale design verification and operation performance. Optimized for space and connectivity, S2C prodigy logic matrix is designed for multi-system expansion to support billions of ASIC gate capacity. This platform is ideal for addressing the ever-increasing complexity and performance requirements in large-scale SoC designs for applications such as 5G, data center, AI/ML, and autonomous driving.

Industry-leading density and capacity-up to 3.136 billion ASIC gates in single standard server rack

Hierarchical connectivity to support flexible topology and hyperscale design validation at prototyping performance

Highly modular design to simplify deployment, maintenance, and expansion in standard server racks

Multi-usages: early software development, full system prototyping, high performance regression

| Logic Matrix LX2 Configuration Table | ||||

| LX2-M1 | LX2-M2 | LX2-P3 | LX2-P4 | |

| Estimated ASIC Gates (M) | 98 | 196 | 294 | 392 |

| FPGAs | 2 * XCVU19P | 4 * XCVU19P | 6 * XCVU19P | 8 * XCVU19P |

| System Logic Cell (K) | 17,876 | 35,752 | 53,628 | 71,504 |

| FPGA Memory (Mb) | 331.8 | 663.6 | 995.4 | 1327.2 |

| DSP Slices | 7,680 | 15,360 | 23,040 | 30,720 |

| User I/Os | 2,912 | 5,824 | 8,736 | 11,648 |

| High-speed Transceiver | 160 | 320 | 480 | 640 |

| Prodigy Connectors (144 IOs) | 18 | 36 | 54 | 72 |

| MCIO Connectors (4 GTY + 8 IOs) | 40 | 80 | 120 | 160 |

| DataSheet | Download | |||

| Logic Matrix LX1 Configuration Table | ||||

| LX1-11 | LX1-21 | LX1-31 | LX1-41 | |

| Estimated ASIC Gates (M) | 60 | 120 | 180 | 240 |

| FPGAs | 2 * XCVU440 | 4 * XCVU440 | 6 * XCVU440 | 8 * XCVU440 |

| System Logic Cell (K) | 11,080 | 22,160 | 33,240 | 44,320 |

| FPGA Memory (Mb) | 177.2 | 354.4 | 531.6 | 708.8 |

| DSP Slices | 5,760 | 11,520 | 17,280 | 23,040 |

| User I/Os | 2,496 | 4,992 | 7,488 | 9,984 |

| GTH Transceivers | 96 | 192 | 288 | 384 |

| Prodigy Connectors (144 IOs) | 16 | 32 | 48 | 64 |

| PGT Connectors (8 GTH + 8 IOs) | 2 | 4 | 6 | 8 |

| MSAS Connectors (4 GTH + 8 IOs) | 20 | 40 | 60 | 80 |

| DataSheet | Download | |||

Logic Matrix address high-performance fpga prototyping by providing a flexible connectivity architecture with 3 levels of hierarchy: ShortBridge with interconnection modules between neighboring FPGAs; SysLink to connect FPGAs over high bandwidth cables, and TransLink for longer distance links between FPGA SerDes over MCIO cables.

More usable gates per FPGA means fewer FPGAs, fewer FPGA interconnects, and higher performance for the same prototyped design. With an estimated gate capacity of 392 million gates per LX2, a fully populated standard server rack with 8 LX2's enables an estimated prototyping capacity of over 3 billion ASIC gates.

Hyperscale designs now range into the billions of ASIC gates. Although these complex designs are demanding, LX2 combines the largest FPGA available from Xilinx with an architecture designed for interconnect optimization, using fpga xilinx board. Constructed to ensure high reliability and robust operation, the LX2 addresses enterprise-class considerations including real-time system monitors, efficient cooling, and redundant hot-pluggable power supplies.