by Daniel Nenni on 04-11-2024 at 6:00 am

Categories: EDA, Prototyping, RISC-V, S2C EDA

RISC-V's popularity stems from its open-source framework, enabling customization, scalability, and mitigating vendor lock-in. Supported by a robust community, its cost-effectiveness and global adoption make it attractive for hardware innovation across industries.

Despite its popularity, evolving RISC-V architectures pose design and verification challenges. A significant concern is the potential fragmentation in RISC-V system integration. Exploring RISC-V microarchitectures may result in variants incompatible with each other. Moreover, as the RISC-V ecosystem matures, design complexity escalates, necessitating enhanced verification procedures.

S2C plays a pivotal role in the RISC-V ecosystem as a member of RISC-V International. Let’s explore how S2C aids chip designers in optimizing and differentiating their RISC-V processor-based SoCs across diverse applications.

S2C has been successfully delivering rapid SoC prototyping solutions since 2003 with over 600 customers, including 6 of the world's top 10 semiconductor companies. I personally have been involved with the prototyping market for a good part of my career and know S2C intimately.

Key Benefits of the S2C FPGA Prototyping Solution for RISC-V

S2C offers an extensive array of FPGA prototyping systems, ranging from the desktop prototyping platform Prodigy Logic System to the high-performance enterprise prototyping solution Logic Matrix, catering to the diverse needs of RISC-V System Verification or Demonstration. Multiple options are available to meet the diversity of RISC-V, regardless of the scale of the design. In addition to traditional partitioning schemes, S2C also provides ChipLink IP, which ensures high-performance AXI chip-to-chip partitioning.

Robust bring-up and debugging methods enhance user efficiency, including FPGA download via Ethernet/USB/SD card, UART/Virtual UART, Ethernet-based AXI transactor, and a custom logic analyzer for Multi-FPGA (MDM).

S2C also provides a utility to download operating systems & applications from PC to FPGA's DDR4.

The high-bandwidth transmission enables a much faster boot-up of software, accelerating time to operation.

General Purpose Partitioning and ChipLink

S2C offers a General-Purpose TDM interconnect communication solution, which is applicable regardless of IP logic scale or bus interface type limitations. Configured as a 25Gbps Line Rate, S2C’s General-Purpose Serdes TDM IP can provide up to 20MHz of TDM partitioning for large IP design partitions. With a multiplexing ratio of up to 8K:1, it enables long-distance data communication via optical fiber cables, streamlining the networking process for large-scale SoC prototype designs with simplicity and efficiency.

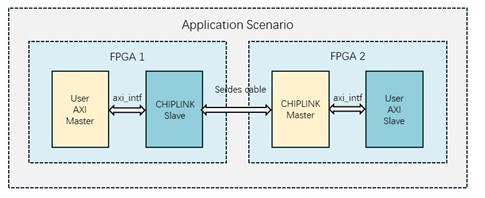

ChipLink, an AXI-based partitioning solution, facilitates multi-core SoC verification. This low-latency AXI Chip to Chip IP connects RISC-V cores and peripherals across multiple FPGAs efficiently. S2C's ChipLink AXI IP boasts high speed and low latency, supporting AXI DATA_WIDTH of up to 1024 bits. Each bank accommodates up to four sets of AXI protocols. With multiple Serdes line rates including 12.5G, 16.25G, 20.625G, and 25G, it enables communication at 100MHz between multi-core processors.

Strengthened by a Broad Prototype Tools

S2C offers a comprehensive suite of tools to facilitate and optimize RISC-V SoC design verification. Notably, Prototype Ready IP features over 90 readily deployable daughter cards, simplifying prototyping setup and significantly reducing initialization time and effort.

Additionally, S2C's multidimensional prototyping software, Prodigy PlayerPro-RT, enables seamless FPGA/Die downloads via USB, Ethernet, and SD Card interfaces. Beyond downloads, PlayerPro-RT offers real-time hardware monitoring, remote system management, and extensive hardware self-testing functionalities, ensuring a smooth and efficient verification process.

S2C further enhances verification with the inclusion of the high-bandwidth AXI transactor, Prodigy ProtoBridge, facilitating swift and efficient data transmission between PC and FPGA prototypes at PCIe speeds of up to 4000MB/s. By offering high bandwidth and fast read/write capabilities, ProtoBridge significantly boosts design productivity.

In the competitive realm of RISC-V SoC development, differentiation is crucial. S2C Prototyping Solutions emerge as a trusted ally, offering a streamlined pathway for verification and demonstration, empowering developers to amplify the unique value propositions of their SoCs.

For more information: https://www.s2cinc.com/riscv.html